Qualcomm Technologies, Inc.

# PM8916/PM8916-1 Power Management ICs

**Device Specification**

LM80-P0436-35 Rev.C March 13, 2018

All Qualcomm products mentioned herein are products of Qualcomm Technologies, Inc. and/or its subsidiaries.

Qualcomm is a trademark of Qualcomm Incorporated, registered in the United States and other countries. Other product and brand names may be trademarks or registered trademarks of their respective owners.

Use of this document is subject to the license set forth in Exhibit 1.

Qualcomm Technologies, Inc. 5775 Morehouse Drive San Diego, CA 92121 U.S.A.

# **Revision history**

| Revision | Date           | Description                                                                                                                                                                                                        |

|----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Α        | August 2015    | Initial release                                                                                                                                                                                                    |

| В        | September 2016 | Updated to E part                                                                                                                                                                                                  |

| С        | March 2018     | <ul> <li>3.7.4.2 19.2 MHz XO crystal requirements: Corrected reference document title and number</li> <li>3.9.1 Poweron circuits and the power sequences: Corrected reference document title and number</li> </ul> |

# Contents

| 1 Ir | ntroduction                                               | 8  |

|------|-----------------------------------------------------------|----|

|      | 1.1 Documentation overview                                | 8  |

|      | 1.2 PM8916 introduction                                   |    |

|      | 1.3 PM8916 features                                       |    |

|      | 1.3.1 Highlighted features integrated into the PM8916     |    |

|      | 1.3.2 Summary of PM8916 device features                   |    |

|      | 1.4 Terms and acronyms                                    | 13 |

|      | 1.5 Special marks                                         | 14 |

| 2 P  | Pad Definitions                                           | 16 |

|      | 2.1 I/O parameter definitions                             | 17 |

|      | 2.2 Pad descriptions                                      |    |

| 3 E  | Electrical Specifications                                 | 26 |

|      | 3.1 Absolute maximum ratings                              |    |

|      | 3.2 Operating conditions                                  | 27 |

|      | 3.3 DC power consumption                                  |    |

|      | 3.4 Digital logic characteristics                         | 29 |

|      | 3.5 Input power management                                | 29 |

|      | 3.5.1 Over-voltage protection                             |    |

|      | 3.5.2 External supply detection                           | 29 |

|      | 3.5.3 Linear battery charger                              | 31 |

|      | 3.5.4 Battery voltage monitoring system                   |    |

|      | 3.5.5 Voltage mode battery monitoring system (VM-BMS)     | 32 |

|      | 3.5.6 Battery interface parameters (BTM and BPD)          |    |

|      | 3.6 Output power management                               |    |

|      | 3.6.1 Reference circuit                                   |    |

|      | 3.6.2 Buck SMPS                                           |    |

|      | 3.6.3 Linear regulators                                   |    |

|      | 3.6.4 Internal voltage-regulator connections              |    |

|      | 3.7 General housekeeping                                  |    |

|      | 3.7.1 Analog multiplexer and scaling circuits             | 51 |

|      | 3.7.2 AMUX input to ADC output end-to-end accuracy        | 54 |

|      | 3.7.3 HK/XO ADC circuit                                   |    |

|      | 3.7.4 System clocks                                       |    |

|      | 3.7.5 Real-time clock                                     | 60 |

|      | 3.7.6 Over-temperature protection (smart thermal control) |    |

|      | 3.8 User interfaces                                       |    |

|      | 3.8.1 Current drivers                                     |    |

|      | 3.8.2 Vibration motor driver                              |    |

|      | 3.9 IC-level interfaces                                   |    |

|      | 3.9.1 Poweron circuits and the power sequences            |    |

|      | 3.9.2 OPT [2:1] hardwired controls                        |    |

|      | 3.9.3 SPMI and the interrupt managers                     |    |

|      | 3.11 Multipurpose pad specifications                      |    |

|      | ο. ε ενισιαραιρόσε ραν ορεοιποαποιο                       |    |

| 3.12 Audio codec                                          | 68 |

|-----------------------------------------------------------|----|

| 3.12.1 Audio inputs and Tx processing                     | 68 |

| 3.12.2 Audio outputs and Rx processing                    | 70 |

| 3.12.3 Support circuits                                   | 74 |

| 4 Mechanical Information                                  | 75 |

| 4.1 Device physical dimensions                            | 75 |

| 4.2 Part marking                                          | 77 |

| 4.2.1 Specification-compliant devices                     | 77 |

| 4.3 Device ordering information                           | 78 |

| 4.3.1 Specification-compliant devices                     | 78 |

| 4.4 Device moisture-sensitivity level                     | 79 |

| 5 Carrier, Storage, and Handling Information              | 80 |

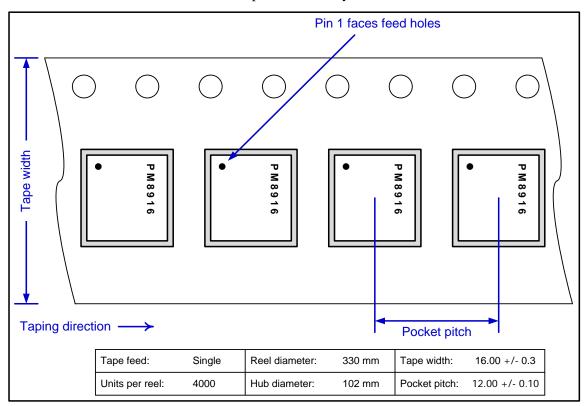

| 5.1 Carrier                                               | 80 |

| 5.1.1 Tape and reel information                           | 80 |

| 5.2 Storage                                               | 81 |

| 5.2.1 Bagged storage conditions                           | 81 |

| 5.2.2 Out-of-bag duration                                 | 81 |

| 5.3 Handling                                              |    |

| 5.3.1 Baking                                              |    |

| 5.3.2 Electrostatic discharge                             | 81 |

| 6 PCB Mounting Guidelines                                 | 83 |

| 6.1 RoHS compliance                                       | 83 |

| 6.2 SMT parameters                                        | 83 |

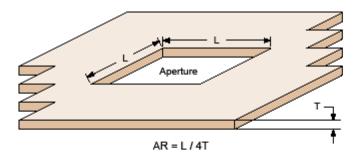

| 6.2.1 Land pad and stencil design                         | 83 |

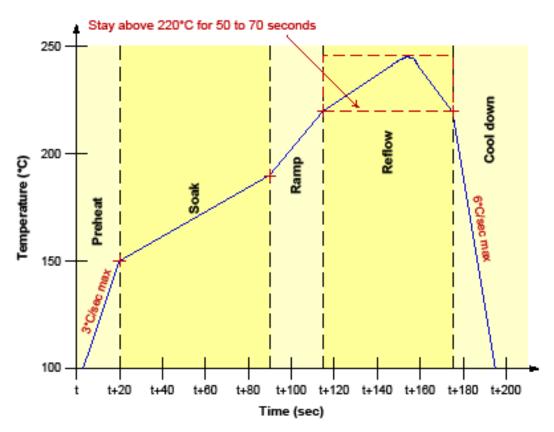

| 6.2.2 Reflow profile                                      |    |

| 6.2.3 SMT peak package-body temperature                   |    |

| 6.2.4 SMT process verification                            |    |

| 6.3 Board-level reliability                               | 86 |

| 7 Part Reliability                                        | 87 |

| 7.1 Reliability qualifications summary                    | 87 |

| 7.1.1 PM8916 reliability evaluation report for NSP device |    |

| 7.2 Qualification sample description                      |    |

# **Figures**

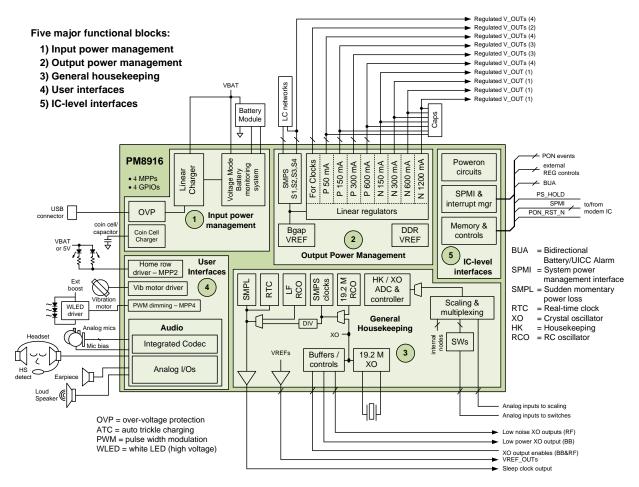

| Figure 1-1 High-level PM8916 functional block diagram                        | 10 |

|------------------------------------------------------------------------------|----|

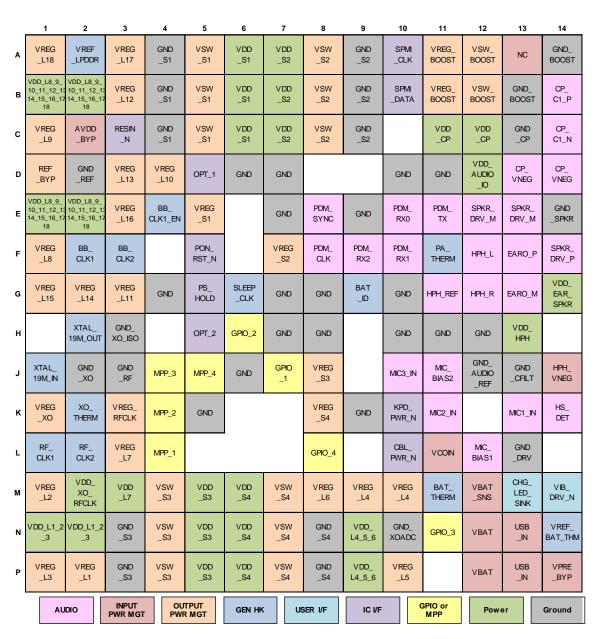

| Figure 2-1 PM8916 pad assignments (top view)                                 |    |

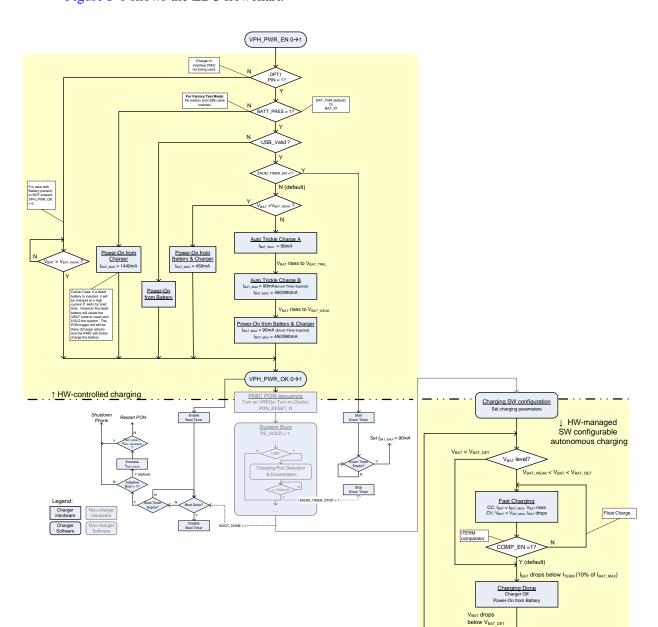

| Figure 3-1 LBC flowchart                                                     |    |

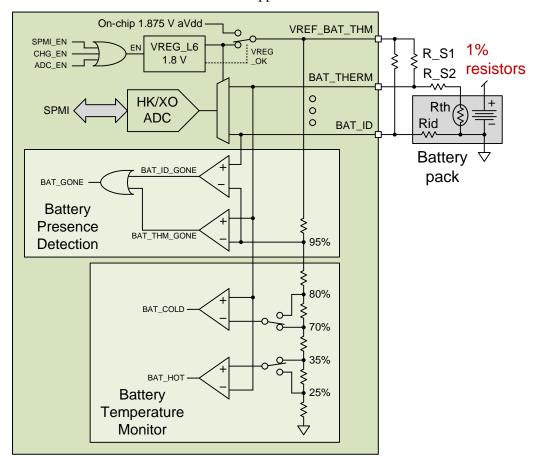

| Figure 3-2 Battery-temperature monitoring                                    | 36 |

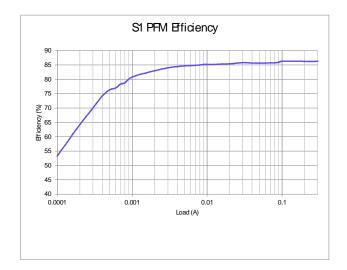

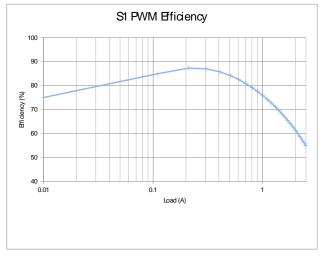

| Figure 3-3 S1 PFM efficiency plots                                           |    |

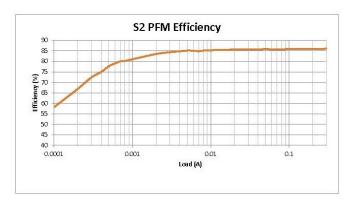

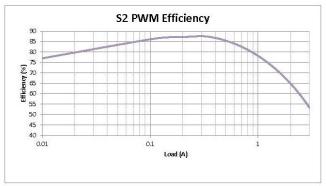

| Figure 3-4 S2 PFM efficiency plots                                           |    |

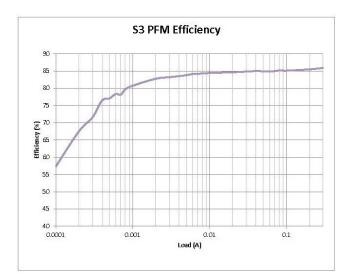

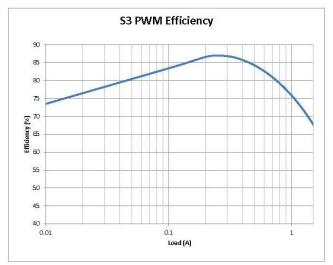

| Figure 3-5 S3 PFM efficiency plots                                           |    |

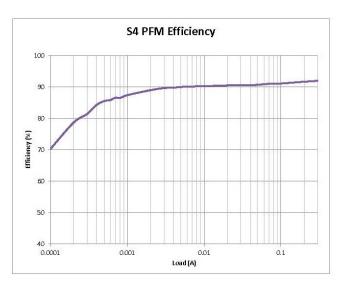

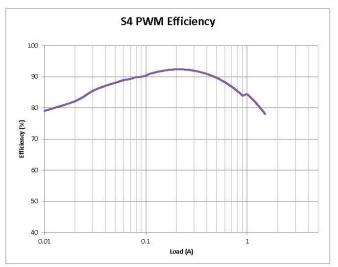

| Figure 3-6 S4 PFM efficiency plots                                           |    |

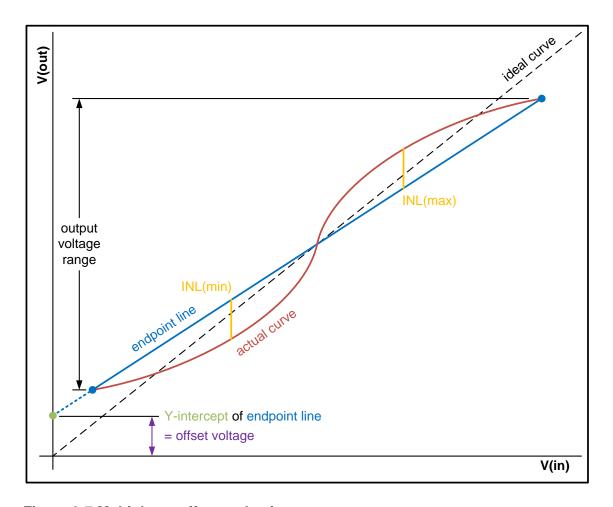

| Figure 3-7 Multiplexer offset and gain errors                                |    |

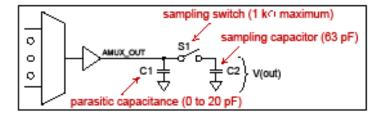

| Figure 3-8 Analog-multiplexer load condition for settling time specification |    |

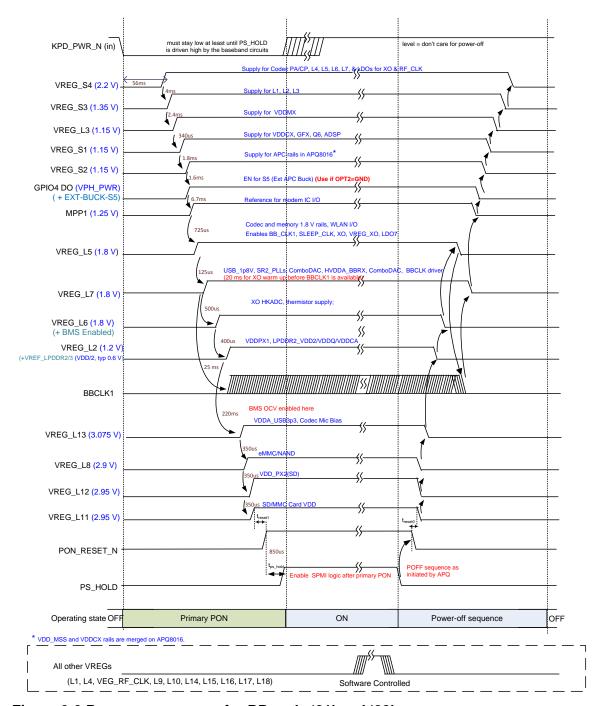

| Figure 3-9 Poweron sequence for BB code '01' and '02'                        |    |

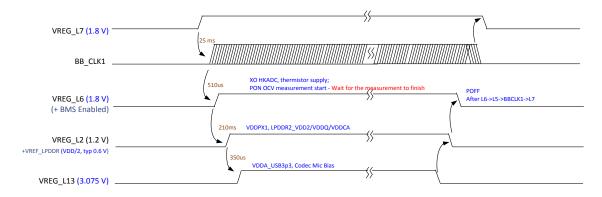

| Figure 3-10 Poweron sequence for BB code 'VV'                                |    |

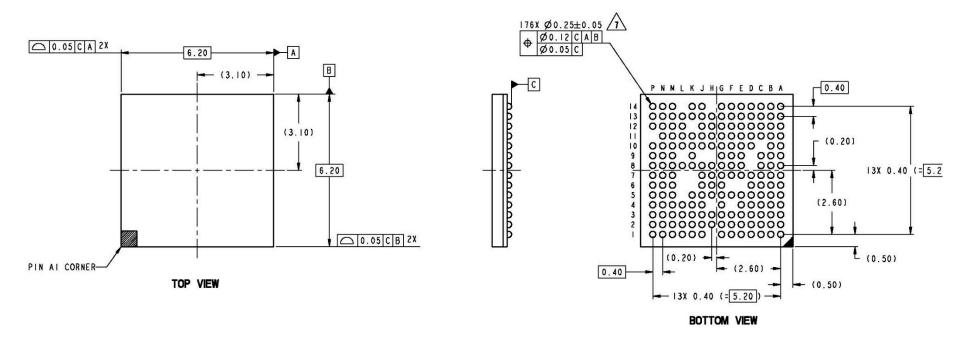

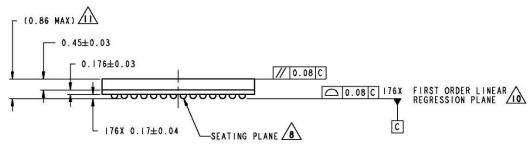

| Figure 4-1 6.2 x 6.2 x 0.86 mm outline drawing                               |    |

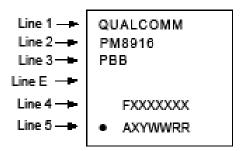

| Figure 4-2 PM8916 device marking (top view, not to scale)                    |    |

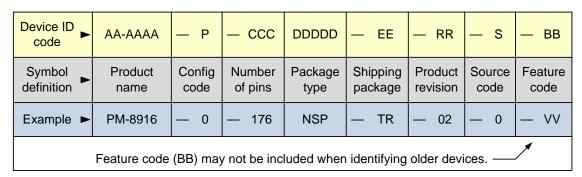

| Figure 4-3 Device identification code                                        |    |

| Figure 5-1 Carrier tape drawing with part orientation                        | 80 |

| Figure 5-2 Tape handling                                                     |    |

| Figure 6-1 Stencil printing aperture area ratio (AR)                         |    |

| Figure 6-2 Acceptable solder-paste geometries                                |    |

| Figure 6-3 QTI typical SMT reflow profile                                    |    |

| •                                                                            |    |

# **Tables**

| Table 1-1 Primary PM8916 device documentation                            | 8  |

|--------------------------------------------------------------------------|----|

| Table 1-2 PM8916 device features                                         | 11 |

| Table 1-3 Terms and acronyms                                             | 13 |

| Table 1-4 Special symbols                                                | 14 |

| Table 2-1 I/O description (pad type) parameters                          | 17 |

| Table 2-2 Pad descriptions – Input power management functions            | 18 |

| Table 2-3 Pad descriptions – output power management functions           | 19 |

| Table 2-4 Pad descriptions – general housekeeping functions              | 20 |

| Table 2-5 Pad descriptions – User interface functions                    | 21 |

| Table 2-6 Pad descriptions – Audio                                       |    |

| Table 2-7 Pad descriptions – IC-level interface functions                | 22 |

| Table 2-8 Pad descriptions – configurable input/output functions         | 23 |

| Table 2-9 Pad descriptions – input DC power                              | 24 |

| Table 2-10 Pad descriptions – grounds                                    | 25 |

| Table 3-1 Absolute maximum ratings                                       | 26 |

| Table 3-2 Operating conditions                                           |    |

| Table 3-3 DC power supply currents                                       | 28 |

| Table 3-4 Audio power supply peak current                                | 28 |

| Table 3-5 Digital I/O characteristics                                    | 29 |

| Table 3-6 External source interface performance specifications           | 30 |

| Table 3-7 Linear charger specifications                                  | 31 |

| Table 3-8 Trickle charging performance specifications                    | 31 |

| Table 3-9 UVLO performance specifications                                | 34 |

| Table 3-10 SMPL performance specifications                               | 34 |

| Table 3-11 Battery fuel-gauge specifications                             | 34 |

| Table 3-12 State of charge (SOC) specifications                          | 35 |

| Table 3-13 Battery interface specifications                              |    |

| Table 3-14 Battery-temperature monitoring calculations                   | 37 |

| Table 3-15 Coin cell charging performance specifications                 | 37 |

| Table 3-16 Regulator high-level summary                                  | 39 |

| Table 3-17 Voltage-reference performance specifications                  | 42 |

| Table 3-18 SMPS performance specifications                               | 43 |

| Table 3-19 LDO performance specifications                                |    |

| Table 3-20 Internal voltage regulator connections                        | 50 |

| Table 3-21 Boost specifications                                          | 50 |

| Table 3-22 Analog multiplexer and scaling functions                      | 51 |

| Table 3-23 Analog multiplexer performance specifications                 |    |

| Table 3-24 AMUX input to ADC output end-to-end accuracy                  | 54 |

| Table 3-25 HK/XO ADC performance specifications                          | 57 |

| Table 3-26 XO controller, buffer, and circuit performance specifications | 58 |

| Table 3-27 RC oscillator performance specifications                      | 59 |

| Table 3-28 RTC performance specifications                                | 60 |

| Table 3-29 Vibration motor driver performance specifications             | 61 |

| Table 3-30 Poweron circuit performance specifications                    |    |

| Table 3-31 OPT_1 and OPT_2 PON parameters                                |    |

| Table 3-32 Programmable GPIO configurations                              | 66 |

| Table 3-33 VOL and VOH for different driver strengths                    |    |

| Table 3-34 Multipurpose pad performance specifications                   |    |

| Table 3-35 Analog microphone input performance                           |    |

| Table 3-36 Ear output performance, 32 Ω load unless specified            |    |

| Table 3-37 HPH output performance 16 O load unless specified             |    |

| Γable 3-38 Mono speaker driver outputs performance, 8 $\Omega$ load and + 12 dB gain unless otherwise specified | 73 |

|-----------------------------------------------------------------------------------------------------------------|----|

| Fable 3-39 Microphone bias specifications                                                                       | 74 |

| Fable 4-1 PM8916 device marking line definitions                                                                | 77 |

| Fable 4-2 PM8916 device identification details                                                                  | 78 |

| Fable 4-3 Feature codes                                                                                         | 78 |

| Fable 4-4 Source configuration code                                                                             | 79 |

| Fable 6-1 QTI typical SMT reflow-profile conditions (for reference only)                                        | 84 |

| Fable 7-1 Silicon reliability results for SMIC                                                                  | 87 |

| Table 7-2 Silicon reliability results for TSMC                                                                  | 8  |

| Table 7-3 Package reliability results for SMIC/TSMC                                                             | 89 |

# 1 Introduction

#### 1.1 Documentation overview

This document contains a description of the chipset capabilities. Not all features are available, nor are all features supported in the software.

NOTE: Enabling some features may require additional licensing fees.

Technical information for PM8916 is primarily covered by the documents listed in Table 1-1, and all should be studied for a thorough understanding of the IC and its applications.

Table 1-1 Primary PM8916 device documentation

| Document number                  | Title/description                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LM80-P0436-34                    | PM8916/PM8916-1 Device Revision Guide Provides a history of PM8916 revisions. It explains how to identify the various IC revisions and discusses known issues (or bugs) for each revision and how to work around them.                                                                                                                              |

| LM80-P0436-35<br>(this document) | PM8916/PM8916-1 Device Specification Provides all PM8916 electrical and mechanical specifications. Additional material includes pad assignment definitions; shipping, storage, and handling instructions; PCB mounting guidelines; and part reliability. This document can be used by the company purchasing departments to facilitate procurement. |

This PM8916 device specification is organized as follows:

Chapter 1 – Provides an overview of PM8916 documentation, shows a high-level PM8916 functional block diagram, lists the device features, and lists terms and acronyms used throughout the document.

- Chapter 2 Defines the IC pad assignments.

- Chapter 3 Defines the IC electrical performance specifications, including absolute maximum ratings and recommended operating conditions.

- Chapter 4 Provides IC mechanical information, including dimensions, markings, ordering information, moisture sensitivity, and thermal characteristics.

- Chapter 5 Discusses shipping, storage, and handling of PM8916 devices.

- Chapter 6 Presents procedures and specifications for mounting the PM8916 onto printed circuit boards (PCBs).

Chapter 7 – Presents PM8916 reliability data, including definitions of the qualification samples and a summary of qualification test results.

### 1.2 PM8916 introduction

The PM8916 device (Figure 1-1) integrates all wireless handset power management, general housekeeping, and user interface support functions into a single mixed-signal IC. Its versatile design is suitable for multimode, multiband phones, and other wireless products such as data cards and PDAs.

The PM8916 mixed-signal HV-CMOS device is available in the 176-pad nanoscale package (NSP) that includes several ground pads for improved electrical ground, mechanical stability, and thermal continuity.

PM8916 supports APQ8016E platforms and PM8916-1 supports APQ8009 platforms. The only difference between PM8916 and PM8916-1 is the default power-on voltage settings.

Since the PM8916 device includes many diverse functions, its operation can be understood better by studying the major functional blocks individually. Therefore, the PM8916 document set is organized by the device functionality as follows:

- Input power management

- Output power management

- General housekeeping

- User interfaces

- IC interfaces

- Configurable pads either multipurpose pads (MPPs) or general-purpose input/output (GPIOs) that can be configured to function within some of the other categories.

Most of the information contained in this document is organized accordingly – including the circuit groupings within the block diagram (Figure 1-1), pad descriptions (Chapter 2), and detailed electrical specifications (Chapter 3).

Figure 1-1 High-level PM8916 functional block diagram

### 1.3 PM8916 features

NOTE: Some of the hardware features integrated within the PM8916 must be enabled through the host IC software. Refer to the latest version of the applicable software release notes to identify the enabled PMIC features.

### 1.3.1 Highlighted features integrated into the PM8916

- Dual SIM dual active (DSDA) support

- Bidirectional battery UICC alarm (BUA) for graceful UICC shutdown upon battery or UICC removal.

- Linear battery charger

- □ USB source with built-in 16 V over-voltage protection (OVP)

- □ Integrated OVP FET

- Four GPIOs of which two can output high-speed clocks

- Pulse width modulator (PWM) for dimming control of external WLED IC driver

- Home row LED driver

- Plug-and-play support

- Programmable reset control

- Audio codec (ADCs and DACs), stereo head phone, ear and speaker amplifiers. The digital decimator and interpolator chains exist in the corresponding APQ8016EAPQ8009 processors.

### 1.3.2 Summary of PM8916 device features

Table 1-2 lists the features of the PM8916 device.

Table 1-2 PM8916 device features

| Feature                                   | PM8916 capability                                                                                                                  |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Input power management                    |                                                                                                                                    |

| Supported external power source           | USB                                                                                                                                |

| Over-voltage protection                   | Fully integrated up to +16 V (integrated OVP FET)                                                                                  |

| Supported battery technologies            | Lithium-ion, lithium-ion polymer                                                                                                   |

| Charger regulation method                 | Linear battery charger  Autonomous charging modes Trickle charging                                                                 |

| Supported charging modes                  | Trickle, constant current, and constant voltage modes.<br>Enhanced automation for lesser software interaction                      |

| Charger on indication                     | Dedicated charging indication LED current sink                                                                                     |

| Voltage, current, and temperature sensors | Internal and external nodes; reported to on-chip state-machine                                                                     |

| Battery monitoring system                 | Voltage Mode Battery Monitoring system (VM-BMS)                                                                                    |

| Coin cell or capacitor backup             | Keep-alive power source; orchestrated charging                                                                                     |

| Output voltage regulation                 |                                                                                                                                    |

| Switched-mode power supplies:             | <ul><li>Four buck converters</li><li>One 5 V boost converter</li></ul>                                                             |

| Low dropout linear regulators             | <ul> <li>20 LDOs</li> <li>Three NMOS LDOs</li> <li>15 PMOS LDOs</li> <li>Two custom low-noise LDOs for the clock system</li> </ul> |

| Pseudo-capless LDO designs                | All LDOs except L1, L2, and L3                                                                                                     |

| LPDDR support                             | Reference voltage output for LPDDR2/LPDDR3                                                                                         |

| General housekeeping                      |                                                                                                                                    |

| On-chip ADC                               | Shared housekeeping (HK) and XO support                                                                                            |

| Feature                                         | PM8916 capability                                                                                                                                                 |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog multiplexing for ADC  HK inputs XO input | <ul> <li>Many internal nodes and external inputs, including configurable MPPs</li> <li>Dedicated pad (XO_THERM)</li> </ul>                                        |

| Over-temperature protection                     | Multistage smart thermal control                                                                                                                                  |

| 19.2 MHz oscillator support                     | XO (with on-chip ADC)                                                                                                                                             |

| XO controller and XO outputs                    | Four sets:  Two low-noise RF outputs Two low-power baseband outputs                                                                                               |

| Sleep clock output                              | One (dedicated)                                                                                                                                                   |

| 32 kHz clock source                             | XO/586 and RC CAL circuits provide real-time clock with alarm. 32,768 Hz crystal oscillator is not supported.                                                     |

| Real-time clock                                 | RTC clock circuits and alarms                                                                                                                                     |

| Audio inputs                                    | <ul><li>Three single-ended inputs</li><li>Two ADCs</li></ul>                                                                                                      |

| Multi-button headset control (MBHC)             | <ul><li>Up to five button MBHC headset support</li><li>One input for headset jack detection</li></ul>                                                             |

| Audio outputs                                   | <ul> <li>Four outputs – Ear, HPHL + HPHR, Class-D speaker driver</li> <li>Three DACs</li> <li>Over current protection on HPH, EAR, and speaker outputs</li> </ul> |

| Multiple input/output audio sample rates        | Supports sample rates 8 kHz, 16 kHz, 32 kHz, and 48 kHz                                                                                                           |

| User interfaces                                 |                                                                                                                                                                   |

| Pulse width modulator                           | Dimming control of external WLED driver                                                                                                                           |

| Home row LED driver                             | Current sink through even MPPs                                                                                                                                    |

| Other current drivers                           | Even MPPs can be configured to sink up to 40 mA ATC indicator (see input power management features)                                                               |

| Vibration motor driver                          | 1.2 to 3.1 V in 100 mV increments                                                                                                                                 |

| IC-level interfaces                             | ,                                                                                                                                                                 |

| Primary status and control                      | 2-line SPMI                                                                                                                                                       |

| Interrupt managers                              | Supported by SPMI                                                                                                                                                 |

| Optional hardware configurations                | OPT bits select hardware configuration                                                                                                                            |

| Power sequencing                                | Power on, power off, and soft resets                                                                                                                              |

| Extra features                                  | External regulator; detects inputs; battery-enabled UICC alarm; UIM support (x2)                                                                                  |

| Feature                    | PM8916 capability                                                                                                                                                                                            |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Configurable I/Os          | Configurable I/Os                                                                                                                                                                                            |  |

| MPPs                       | Four; configurable as digital in/out; unidirectional level-translating I/Os; analog multiplexer inputs; current sinks; VREF buffer outputs; MPP1 and MPP3 is fixed for VDD_PX_BIAS and VREF_DAC respectively |  |

| GPIO pads                  | Four; configurable as digital inputs or outputs or level-translating I/Os; all are faster than MPPs                                                                                                          |  |

| Package                    |                                                                                                                                                                                                              |  |

| Size                       | 6.2 mm × 6.2 mm                                                                                                                                                                                              |  |

| Pad count and package type | 176 pad WB-NSP                                                                                                                                                                                               |  |

# 1.4 Terms and acronyms

Table 1-3 defines terms and acronyms used throughout this document.

**Table 1-3 Terms and acronyms**

| Term or acronym | Definition                                    |

|-----------------|-----------------------------------------------|

| ADC             | Analog-to-digital converter                   |

| AMSS            | Advanced mobile subscriber station (software) |

| ANC             | Active noise cancellation                     |

| ВОМ             | Bill of materials                             |

| BPF             | Bandpass filter                               |

| bps             | Bits per second                               |

| CDMA            | Code division multiple access                 |

| СР              | Charge pump                                   |

| DAC             | Digital-to-analog converter                   |

| DMIC            | Digital microphone                            |

| DRE             | Dynamic range enhancement                     |

| ESD             | Electrostatic discharge                       |

| ESR             | Effective series resistance                   |

| I2C             | Inter-integrated circuit                      |

| 12S             | Inter-IC sound                                |

| IIR             | Infinite impulse response                     |

| kbps            | Kilobits per second                           |

| LBC             | Linear battery charger                        |

| LDO             | Low dropout (linear regulator)                |

| LPF             | Low-pass filter                               |

| Term or acronym | Definition                                 |

|-----------------|--------------------------------------------|

| MAD             | Microphone activity detection              |

| MBHC            | Multi-button headset control               |

| MIC or mic      | Microphone                                 |

| NS              | Noise shaper                               |

| NVM             | Nonvolatile memory                         |

| OEM             | Original equipment manufacturer            |

| OSR             | Over-sampling rate                         |

| PA              | Power amplifier                            |

| PCB             | Printed circuit board                      |

| PCM             | Pulse-coded modulation                     |

| PGA             | Programmable gain amplifier                |

| RoHS            | Restriction of hazardous substances        |

| Rx              | Receive, receiver                          |

| SLIMbus         | Serial low-power inter-chip media bus      |

| SMT             | Surface-mount technology                   |

| SNR             | Signal-to-noise ratio                      |

| ST              | Sidetone                                   |

| TCXO            | Temperature-compensated crystal oscillator |

| Tx              | Transmit, transmitter                      |

| VM-BMS          | Voltage mode battery monitoring system     |

| WCD             | WSP coder/decoder                          |

| WLNSP           | Wafer-level nanoscale package              |

| WSP             | Wafer-scale package                        |

| хо              | Crystal oscillator                         |

| ZIF             | Zero intermediate frequency                |

# 1.5 Special marks

Table 1-4 lists some special symbols used in this document.

**Table 1-4 Special symbols**

| Mark | Definition                                                                                                                                                                                                                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| []   | Brackets ([ ]) sometimes follow a pad, register, or bit name. These brackets enclose a range of numbers. For example, DATA [7:4] may indicate a range that is 4 bits in length, or DATA[7:0] may refer to eight DATA pads. |

| _N   | A suffix of _N indicates an active low signal. For example, PON_RESET_N.                                                                                                                                                   |

| Mark   | Definition                                                                                                                                                                                                                                                                      |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0000 | Hexadecimal numbers are identified with an x in the number, (for example, 0x0000). All numbers are decimal (base 10) unless otherwise specified. Non-obvious binary numbers have the term binary enclosed in parentheses at the end of the number [for example, 0011 (binary)]. |

|        | A vertical bar in the outside margin of a page indicates that a change has been made since the previous revision of this document.                                                                                                                                              |

# 2 Pad Definitions

The PM8916 is available in the 176 NSP – see Chapter 4 for package details. Figure 2-1 shows a high-level view of the pad assignments for the PM8916.

Figure 2-1 PM8916 pad assignments (top view)

# 2.1 I/O parameter definitions

Table 2-1 I/O description (pad type) parameters

| Symbol          | Description                                                                                                                                                                             |  |  |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pad attribute   |                                                                                                                                                                                         |  |  |  |  |  |  |

| Al              | Analog input                                                                                                                                                                            |  |  |  |  |  |  |

| AO              | Analog output                                                                                                                                                                           |  |  |  |  |  |  |

| DI              | Digital input (CMOS)                                                                                                                                                                    |  |  |  |  |  |  |

| DO              | Digital output (CMOS)                                                                                                                                                                   |  |  |  |  |  |  |

| PI              | Power input; a pad that handles 10 mA or more of current flow into the device                                                                                                           |  |  |  |  |  |  |

| PO              | Power output; a pad that handles 10 mA or more of current flow out of the device                                                                                                        |  |  |  |  |  |  |

| Z               | High-impedance (high-Z) output                                                                                                                                                          |  |  |  |  |  |  |

| Pad voltage gro | oupings                                                                                                                                                                                 |  |  |  |  |  |  |

| V_INT           | Internally generated supply voltage for some power on circuits                                                                                                                          |  |  |  |  |  |  |

| V_PAD           | Supply for host IC interfaces; connected internally to VREG_L5                                                                                                                          |  |  |  |  |  |  |

| V_XBB           | Supply for XO low-power (BB) output buffers; connected internally to VREG_L7                                                                                                            |  |  |  |  |  |  |

| V_XRF           | Supply for XO low-noise (RF) output buffers; connected internally to LDO VREG_RFCLK                                                                                                     |  |  |  |  |  |  |

| V_G             | Pad voltage grouping (GPIO_1 and GPIO_2 cannot be configured to VBAT supply group)  Selectable supply for GPIO circuits; options include:  0 = VBAT  1 = VBAT  2 = VREG_L2  3 = VREG_L5 |  |  |  |  |  |  |

| V_M             | Selectable supply for MPP circuits; options include:  0 = VBAT  1 = VBAT  2 = VREG_L2  3 = VREG_L5                                                                                      |  |  |  |  |  |  |

| GPIO pad confi  | igurations                                                                                                                                                                              |  |  |  |  |  |  |

| GPIO pads, whe  | en configured as inputs, have configurable pull settings                                                                                                                                |  |  |  |  |  |  |

| NP              | No internal pull enabled                                                                                                                                                                |  |  |  |  |  |  |

| PU              | Internal pull-up enabled                                                                                                                                                                |  |  |  |  |  |  |

| PD              | PD Internal pull-down enabled                                                                                                                                                           |  |  |  |  |  |  |

| GPIO pads, who  | en configured as outputs, have configurable drive strengths                                                                                                                             |  |  |  |  |  |  |

| Н               | High: ~ 0.9 mA at 1.8 V; ~ 1.9 mA at 2.6 V                                                                                                                                              |  |  |  |  |  |  |

| M               | Medium: ~ 0.6 mA at 1.8 V; ~ 1.25 mA at 2.6 V                                                                                                                                           |  |  |  |  |  |  |

| L               | Low: ~ 0.15 mA at 1.8 V; ~ 0.3 mA at 2.6 V                                                                                                                                              |  |  |  |  |  |  |

# 2.2 Pad descriptions

The following tables list the descriptions of all the respective pads, organized by their functional group:

- Table 2-2 Input power management

- Table 2-3 Output power management

- Table 2-4 General housekeeping

- Table 2-5 User interfaces

- Table 2-6 Audio

- Table 2-7 IC-level interfaces

- Table 2-8 Configurable input/output GPIO and MPPs

- Table 2-9 Power supply pads

- Table 2-10 Ground pads

Table 2-2 Pad descriptions – Input power management functions

|                  | Pad name                        | Pad name           | Pad charac | teristics1 |                                                                                                          |  |  |  |

|------------------|---------------------------------|--------------------|------------|------------|----------------------------------------------------------------------------------------------------------|--|--|--|

| Pad #            | and/or function                 | or<br>alt function | Voltage    | Type       | Functional description                                                                                   |  |  |  |

| Linear charger   | Linear charger                  |                    |            |            |                                                                                                          |  |  |  |

| N13, P13         | USB_IN                          |                    | -          | PI         | Input power from USB source                                                                              |  |  |  |

| C2               | AVDD_BYP                        |                    | _          | AO         | Bypass cap for internal analog circuits                                                                  |  |  |  |

| P14              | VPRE_BYP                        |                    | _          | AO         | VPRE regulator load capacitor                                                                            |  |  |  |

| BMS circuits     |                                 |                    |            |            |                                                                                                          |  |  |  |

| N12, P12         | VBAT                            |                    | _          | PI, PO     | Battery node; input during battery operation, output during charging, and sense point for UVLO detection |  |  |  |

| M12              | VBAT_SNS                        |                    | _          | Al         | Main battery voltage sense point for VM-BMS, Vtrkl, VDD_MAX, and VBAT_WEAK                               |  |  |  |

| Coin cell or kee | Coin cell or keep-alive battery |                    |            |            |                                                                                                          |  |  |  |

| L11              | VCOIN                           |                    |            | AI, AO     | Sense input or charge output                                                                             |  |  |  |

<sup>&</sup>lt;sup>1</sup>See Table 2-1 for parameter and acronym definition.

Table 2-3 Pad descriptions – output power management functions

|                       | Pad name            | Pad characteristics <sup>1</sup> |    | Functional description             |  |

|-----------------------|---------------------|----------------------------------|----|------------------------------------|--|

| Pad #                 | and/or function     | Voltage Type                     |    |                                    |  |

| Switched-mode         | e power supply (SMI | PS) circuits                     |    |                                    |  |

| A5, B5, C5            | VSW_S1              | -                                | РО | Buck converter S1 switching output |  |

| E5                    | VREG_S1             | _                                | Al | Buck converter S1 sense point      |  |

| A8, B8, C8            | VSW_S2              | _                                | PO | Buck converter S2 switching output |  |

| F7                    | VREG_S2             | _                                | Al | Buck converter S2 sense point      |  |

| M4, N4, P4            | VSW_S3              | _                                | PO | Buck converter S3 switching output |  |

| J8                    | VREG_S3             | _                                | Al | Buck converter S3 sense point      |  |

| M7, N7, P7            | VSW_S4              | _                                | PO | Buck converter S4 switching output |  |

| K8                    | VREG_S4             | _                                | Al | Buck converter S4 sense point      |  |

| A12, B12              | VSW_BOOST           | _                                | PI | Boost converter switching net      |  |

| A11, B11              | VREG_BOOST          | _                                | PO | Boost converter output voltage     |  |

| LDO linear regulators |                     |                                  |    |                                    |  |

| P2                    | VREG_L1             | -                                | РО | Linear regulator L1 output         |  |

| M1                    | VREG_L2             | _                                | PO | Linear regulator L2 output         |  |

| P1                    | VREG_L3             | _                                | PO | Linear regulator L3 output         |  |

| M10, M9               | VREG_L4             | _                                | PO | Linear regulator L4 output         |  |

| P10                   | VREG_L5             | _                                | PO | Linear regulator L5 output         |  |

| M8                    | VREG_L6             | _                                | PO | Linear regulator L6 output         |  |

| L3                    | VREG_L7             | _                                | РО | Linear regulator L7 output         |  |

| F1                    | VREG_L8             | _                                | PO | Linear regulator L8 output         |  |

| C1                    | VREG_L9             | _                                | РО | Linear regulator L9 output         |  |

| D4                    | VREG_L10            | _                                | PO | Linear regulator L10 output        |  |

| G3                    | VREG_L11            | _                                | PO | Linear regulator L11 output        |  |

| В3                    | VREG_L12            | _                                | PO | Linear regulator L12 output        |  |

| D3                    | VREG_L13            | _                                | PO | Linear regulator L13 output        |  |

| G2                    | VREG_L14            | _                                | PO | Linear regulator L14 output        |  |

| G1                    | VREG_L15            | _                                | PO | Linear regulator L15 output        |  |

| E3                    | VREG_L16            | _                                | PO | Linear regulator L16 output        |  |

| А3                    | VREG_L17            | _                                | PO | Linear regulator L17 output        |  |

| A1                    | VREG_L18            | _                                | PO | Linear regulator L18 output        |  |

| K3                    | VREG_RFCLK          | _                                | РО | Linear regulator for RF CLK output |  |

<sup>&</sup>lt;sup>1</sup>See Table 2-1 for parameter and acronym definition.

| D-1#                                      | Pad name        | Pad characteristics <sup>1</sup> |      | Formation and descriptions     |  |

|-------------------------------------------|-----------------|----------------------------------|------|--------------------------------|--|

| Pad #                                     | and/or function | Voltage                          | Туре | Functional description         |  |

| K1                                        | VREG_XO         | - PO                             |      | Linear regulator for XO output |  |

| Bandgap voltage reference (VREF) circuits |                 |                                  |      |                                |  |

| D1                                        | REF_BYP         | _                                | AO   | Bandgap reference bypass cap   |  |

Table 2-4 Pad descriptions – general housekeeping functions

| Pad #                                                           | Pad name                                  | Pad name or       | Pad chara          | cteristics1 | Francisco de conjution                 |  |  |  |

|-----------------------------------------------------------------|-------------------------------------------|-------------------|--------------------|-------------|----------------------------------------|--|--|--|

| Pad #                                                           | and/or function                           | alt function      | Voltage            | Туре        | Functional description                 |  |  |  |

| GPIO ass                                                        | ignments for general h                    | nousekeeping func | tions <sup>2</sup> |             |                                        |  |  |  |

| MPP assignments for general housekeeping functions <sup>3</sup> |                                           |                   |                    |             |                                        |  |  |  |

| Analog m                                                        | Analog multiplexer and HK/XO ADC circuits |                   |                    |             |                                        |  |  |  |

| K2                                                              | XO_THERM                                  |                   | _                  | Al          | ADC input – XO thermistor              |  |  |  |

| F11                                                             | PA_THERM                                  |                   | _                  | Al          | AMUX input – PA thermistor output      |  |  |  |

| M11                                                             | BAT_THERM                                 |                   | _                  | Al          | AMUX input – Battery thermistor output |  |  |  |

| G9                                                              | BAT_ID                                    |                   | _                  | Al          | AMUX input – Battery ID                |  |  |  |

| 19.2 MHz                                                        | XO circuits                               |                   |                    |             |                                        |  |  |  |

| J1                                                              | XTAL_19M_IN                               |                   | _                  | Al          | 19.2 MHz crystal input                 |  |  |  |

| H2                                                              | XTAL_19M_OUT                              |                   | _                  | AO          | 19.2 MHz crystal output                |  |  |  |

| L1                                                              | RF_CLK1                                   |                   | V_XRF              | DO          | RF (low-noise) XO output 1             |  |  |  |

| L2                                                              | RF_CLK2                                   |                   | V_XRF              | DO          | RF (low-noise) XO output 2             |  |  |  |

| F2                                                              | BB_CLK1                                   |                   | V_XBB              | DO          | Baseband (low power) XO output 1       |  |  |  |

| F3                                                              | BB_CLK2                                   |                   | V_XBB              | DO          | Baseband (low power) XO output 2       |  |  |  |

| E4                                                              | BB_CLK1_EN                                |                   | V_PAD              | DI          | Baseband XO output 1 enable            |  |  |  |

| Sleep clo                                                       | Sleep clock                               |                   |                    |             |                                        |  |  |  |

| G6                                                              | SLEEP_CLK                                 |                   | V_PAD              | DO          | Sleep clock to host IC and others      |  |  |  |

| VREF out                                                        | puts                                      |                   |                    |             |                                        |  |  |  |

| N14                                                             | VREF_BAT_THM                              |                   | _                  | AO          | Reference voltage for XO thermistor    |  |  |  |

<sup>&</sup>lt;sup>1</sup>See Table 2-1 for parameter and acronym definition

<sup>&</sup>lt;sup>2</sup>GPIOs are used for other general housekeeping functions not listed here; those details will be included in future revisions of this document. To assign a GPIO a particular function, identify the application's requirements and map each GPIO to its function – carefully avoiding assignment conflicts. Table 2-8 lists all the GPIOs.

<sup>&</sup>lt;sup>3</sup>MPPs are used for other general housekeeping functions not listed here; those details will be included in future revisions of this document. To assign an MPP a particular function, identify the application's requirements and map each MPP to its function – carefully avoiding assignment conflicts. Table 2-8 lists all the MPPs.

| Pad #  | Pad name        | Pad name or  | Pad characteristics <sup>1</sup> |      | Functional description                         |

|--------|-----------------|--------------|----------------------------------|------|------------------------------------------------|

| I au # | and/or function | alt function | Voltage                          | Туре | i unctional description                        |

| A2     | VREF_LPDDR      |              | -                                | AO   | Reference voltage for LPDDR 2 / LPDDR 3 memory |

#### Table 2-5 Pad descriptions – User interface functions

|                        | Pad name                                                   | Pad name or              | Pad cha | racteristics1 | Functional description                |  |  |  |

|------------------------|------------------------------------------------------------|--------------------------|---------|---------------|---------------------------------------|--|--|--|

| Pad #                  | and/or function                                            | alt function             | Voltage | Туре          | i unctional description               |  |  |  |

| GPIO as                | GPIO assignments for user interface functions <sup>2</sup> |                          |         |               |                                       |  |  |  |

| MPP ass                | signments for user interfac                                | e functions <sup>3</sup> |         |               |                                       |  |  |  |

| Low-vo                 | Itage current drivers                                      |                          |         |               |                                       |  |  |  |

| M13                    | CHG_LED_SINK                                               |                          | _       | AO            | Charging indication LED driver output |  |  |  |

| Vibration motor driver |                                                            |                          |         |               |                                       |  |  |  |

| M14                    | VIB_DRV_N                                                  |                          | _       | РО            | Vibration motor driver output control |  |  |  |

#### Table 2-6 Pad descriptions – Audio

|          | Pad name        | Pad name or  | Pad chara | cteristics4 |                                   |

|----------|-----------------|--------------|-----------|-------------|-----------------------------------|

| Pad #    | and/or function | alt function | Voltage   | Туре        | Functional description            |

| L12      | MIC_BIAS1       |              | _         | AO          | Microphone bias #1                |

| J11      | MIC_BIAS2       |              | -         | AO          | Microphone bias #2                |

| D13, D14 | CP_VNEG         |              | -         | AO          | Charge pump negative output       |

| B14      | CP_C1_P         |              | -         | AO          | Charge pump fly cap terminal 1    |

| C14      | CP_C1_N         |              | -         | AO          | Charge pump fly cap terminal 2    |

| K13      | MIC1_IN         |              | -         | Al          | Main mic                          |

| K11      | MIC2_IN         |              | -         | Al          | Headset mic                       |

| J10      | MIC3_IN         |              | -         | Al          | Second mic                        |

| K14      | HS_DET          |              | -         | Al          | Headset detection                 |

| F13      | EARO_P          |              | _         | AO          | Earpiece PA + output              |

| G13      | EARO_M          |              | -         | AO          | Earpiece PA – output              |

| F12      | HPH_L           |              | _         | AO          | Headphone PA left channel output  |

| G11      | HPH_REF         |              | -         | Al          | Headphone PA ground sensing       |

| G12      | HPH_R           |              | _         | AO          | Headphone PA right channel output |

<sup>&</sup>lt;sup>1</sup>See Table 2-1 for parameter and acronym definition.

<sup>&</sup>lt;sup>2</sup>GPIOs are used for other general housekeeping functions not listed here; those details will be included in future revisions of this document. To assign a GPIO a particular function, identify the application's requirements and map each GPIO to its function – carefully avoiding assignment conflicts. Table 2-8 lists all the GPIOs.

<sup>&</sup>lt;sup>3</sup>MPPs are used for other general housekeeping functions not listed here; those details will be included in future revisions of this document. To assign an MPP a particular function, identify the application's requirements and map each MPP to its function – carefully avoiding assignment conflicts. Table 2-8 lists all the MPPs.

<sup>&</sup>lt;sup>4</sup>See Table 2-1 for parameter and acronym definitions.

|          | Pad name        | Pad name or  | Pad chara | cteristics4 |                                             |

|----------|-----------------|--------------|-----------|-------------|---------------------------------------------|

| Pad #    | and/or function | alt function | Voltage   | Туре        | Functional description                      |

| F14      | SPKR_DRV_P      |              | -         | AO          | Class-D speaker amp + output                |

| E12, E13 | SPKR_DRV_M      |              | -         | AO          | Class-D speaker amp – output                |

| F8       | PDM_CLK         |              | _         | DI          | PDM clock signal and master clock for codec |

| E8       | PDM_SYNC        |              | -         | DI          | PDM synchronization signal                  |

| E11      | PDM_TX          |              | -         | DO          | PDM Tx data channel                         |

| E10      | PDM_RX0         |              | _         | DI          | PDM RX0 data channel                        |

| F10      | PDM_RX1         |              | -         | DI          | PDM RX1 data channel                        |

| F9       | PDM_RX2         |              | -         | DI          | PDM RX2 data channel                        |

| J14      | HPH_VNEG        |              | -         | Al          | Headphone amplifier negative supply         |

Table 2-7 Pad descriptions – IC-level interface functions

|                                                                | Pad name                                                      | Pad name or      | Pad charac     | cteristics1 |                                       |  |  |  |

|----------------------------------------------------------------|---------------------------------------------------------------|------------------|----------------|-------------|---------------------------------------|--|--|--|

| Pad #                                                          | and/or function                                               | alt function     | Voltage        | Туре        | Functional description                |  |  |  |

| GPIO assignments for IC-level interface functions <sup>2</sup> |                                                               |                  |                |             |                                       |  |  |  |

| MPP assig                                                      | MPP assignments for IC-level interface functions <sup>3</sup> |                  |                |             |                                       |  |  |  |

| Poweron                                                        | circuit inputs                                                |                  |                |             |                                       |  |  |  |

| L10                                                            | CBL_PWR_N                                                     |                  | V_INT          | DI          | Cable poweron detect input            |  |  |  |

| K10                                                            | KPD_PWR_N                                                     |                  | V_INT          | DI          | Keypad poweron detect input           |  |  |  |

| H5                                                             | OPT_2                                                         |                  | V_INT          | DI          | Option HW configuration control bit 2 |  |  |  |

| D5                                                             | OPT_1                                                         |                  | V_INT          | DI          | Option HW configuration control bit 1 |  |  |  |

| G5                                                             | PS_HOLD                                                       |                  | V_PAD          | DI          | Power-supply hold control input       |  |  |  |

| С3                                                             | RESIN_N                                                       |                  | V_INT          | DI          | PMIC reset input                      |  |  |  |

| Poweron                                                        | circuit outputs ar                                            | nd primary PM/ho | st IC interfac | e signals   |                                       |  |  |  |

| A10                                                            | SPMI_CLK                                                      |                  | V_PAD          | DI          | Slave and PBUS interface clock        |  |  |  |

| B10                                                            | SPMI_DATA                                                     |                  | V_PAD          | DI, DO      | Slave and PBUS interface data         |  |  |  |

| F5                                                             | PON_RST_N                                                     |                  | V_PAD          | DO          | Poweron reset output control          |  |  |  |

<sup>&</sup>lt;sup>1</sup>See Table 2-1 for parameter and acronym definitions.

<sup>&</sup>lt;sup>2</sup>GPIOs are used for other general housekeeping functions not listed here; those details will be included in future revisions of this document. To assign a GPIO a particular function, identify the application's requirements and map each GPIO to its function – carefully avoiding assignment conflicts. Table 2-8 lists all the GPIO1s.

<sup>&</sup>lt;sup>3</sup>MPPs are used for other general housekeeping functions not listed here; those details will be included in future revisions of this document. To assign an MPP a particular function, identify the application's requirements and map each MPP to its function – carefully avoiding assignment conflicts. Table 2-8 lists all the MPPs.

Table 2-8 Pad descriptions - configurable input/output functions

|           |                 | Configurable                                | Pad char           | acteristics1               |                                                                                                               |

|-----------|-----------------|---------------------------------------------|--------------------|----------------------------|---------------------------------------------------------------------------------------------------------------|

| Pad #     | Pad name        | function                                    | Voltage            | Туре                       | Functional description                                                                                        |

| Predefine | d MPP functions | s – available only a                        | at the assig       | ned MPPs                   |                                                                                                               |

| L4        | MPP_1           | VDD_PX_BIAS<br>Digital I/O<br>(optional)    | -<br>-<br>V_M      | AO-Z<br>AO<br>DI, DO       | Configurable MPP Reference for host IC I/O Digital input/output usage (optional)                              |

| K4        | MPP_2           | SKIN_TEMP HR_LED_SNK Digital I/O (optional) | -<br>-<br>-<br>V_M | AO-Z<br>AI<br>AI<br>DI, DO | Configurable MPP Skin temperature measurement Home row LED current sink Digital input/output usage (optional) |

| J4        | MPP_3           | VREF_DAC<br>Digital I/O<br>(optional)       | –<br>–<br>V_M      | AO-Z<br>AO<br>DI, DO       | Configurable MPP Reference for host IC DAC Digital input/output usage (optional)                              |

| J5        | MPP_4           | WLED_PWM Digital I/O (optional)             | –<br>V_M<br>V_M    | AO-Z<br>DO<br>DI, DO       | Configurable MPP PWM control for external WLED driver Digital input/output usage (optional)                   |

| Predefine | d GPIO function | ıs – available only                         | at the assi        | gned GPIOs                 |                                                                                                               |

| J7        | GPIO_1          | UIM_BATT_AL<br>M                            | V_G<br>-           | DO-Z<br>DI, DO             | Configurable GPIO Battery removal alarm for UIM and UIM battery alarm input to the APQ                        |

| H6        | GPIO_2          | NFC_CLK_REQ                                 | V_G<br>-           | DO-Z<br>DI                 | Configurable GPIO<br>NFC control signal to request clock                                                      |

| N11       | GPIO_3          | WCN_LDO_EN                                  | V_G<br>-           | DO-Z<br>DO                 | Configurable GPIO Enable signal to power WCN with external 1.35 V LDO in PM8916-1                             |

| L8        | GPIO_4          | EXT_BUCK_EN                                 | V_G<br>-           | DO-Z<br>DO                 | Configurable GPIO Enable signal for external buck converter to power applications core.                       |

NOTE: All MPPs default to their high-Z state at powerup and must be configured after powerup for their intended purposes. All GPIOs default to  $10~\mu\text{A}$  pulldown at powerup and must be configured after powerup for their intended purposes.

NOTE: Configure unused MPPs as 0 mA current sinks (high-Z) and GPIOs as digital inputs with their internal pull-downs enabled.

<sup>&</sup>lt;sup>1</sup>See Table 2-1 for parameter and acronym definitions.

NOTE: Only even MPPs can be configured as current sink and only odd MPPs can be configured as analog output.

Table 2-9 Pad descriptions – input DC power

| Pad #                       | Pad name                                | Functional description                                                                 |

|-----------------------------|-----------------------------------------|----------------------------------------------------------------------------------------|

| N1, N2 <sup>1</sup>         | VDD_L1_2_3                              | Power supply for LDO L1, L2, and L3 circuits                                           |

| N9, P9                      | VDD_L4_5_6                              | Power supply for LDO L4, L5, and L6 circuits                                           |

| B1, B2, E1, E2 <sup>2</sup> | VDD_L8_9_10_11_12_13_<br>14_15_16_17_18 | Power supply for LDO L8 to L18 circuits                                                |

| M2                          | VDD_XO_RFCLK                            | Power supply for LDO VREG_XO and VREG_RFCLK circuits                                   |

| M3                          | VDD_L7                                  | Power supply for LDO L7 circuits                                                       |

| A6, B6, C6                  | VDD_S1                                  | Power supply for S1 buck converter                                                     |

| A7, B7, C7                  | VDD_S2                                  | Power supply for S2 buck converter                                                     |

| M5, N5, P5                  | VDD_S3                                  | Power supply for S3 buck converter                                                     |

| M6, N6, P6                  | VDD_S4                                  | Power supply for S4 buck converter                                                     |

| Audio input power           |                                         |                                                                                        |

| A13                         | NC                                      | Can be connected to VBAT to maintain backward compatibility with version 1.1 of PM8916 |

| H13                         | VDD_HPH                                 | Headphone amplifier positive supply                                                    |

| G14                         | VDD_EAR_SPKR                            | Ear and class-D speaker amplifier supply                                               |

| D12                         | VDD_AUDIO_IO                            | I/O supply for codec                                                                   |

| C11, C12                    | VDD_CP                                  | Charge pump power supply                                                               |

<sup>&</sup>lt;sup>1</sup>Pad N1 and N2 have been combined to same input voltage group from Rev. 2.0.

<sup>&</sup>lt;sup>2</sup>Pads B1, B2 and E1, E2 have been combined to same input voltage group from Rev 2.0.

Table 2-10 Pad descriptions – grounds

| Pad #                                                                                 | Pad name      | Functional description                            |

|---------------------------------------------------------------------------------------|---------------|---------------------------------------------------|

| PM88916                                                                               |               |                                                   |

| A14, B13                                                                              | GND_BOOST     | Boost ground net                                  |

| D6, D7, D10, D11,<br>E7, E9, G4, G7, G8,<br>G10, H7, H8, H10,<br>H11, H12, J6, K5, K9 | GND           | Ground for non-specialized circuits               |

| L13                                                                                   | GND_DRV       | Ground for vibrator driver                        |

| D2                                                                                    | GND_REF       | Ground for bandgap reference circuit              |

| A4, B4, C4                                                                            | GND_S1        | Ground for S1 buck converter circuits             |

| A9, B9, C9                                                                            | GND_S2        | Ground for S2 buck converter circuits             |

| N3, P3                                                                                | GND_S3        | Ground for S3 buck converter circuits             |

| N8, P8                                                                                | GND_S4        | Ground for S4 buck converter circuits             |

| J2                                                                                    | GND_XO        | Ground for XO circuits                            |

| J3                                                                                    | GND_RF        | Ground for RF circuits                            |